Overview

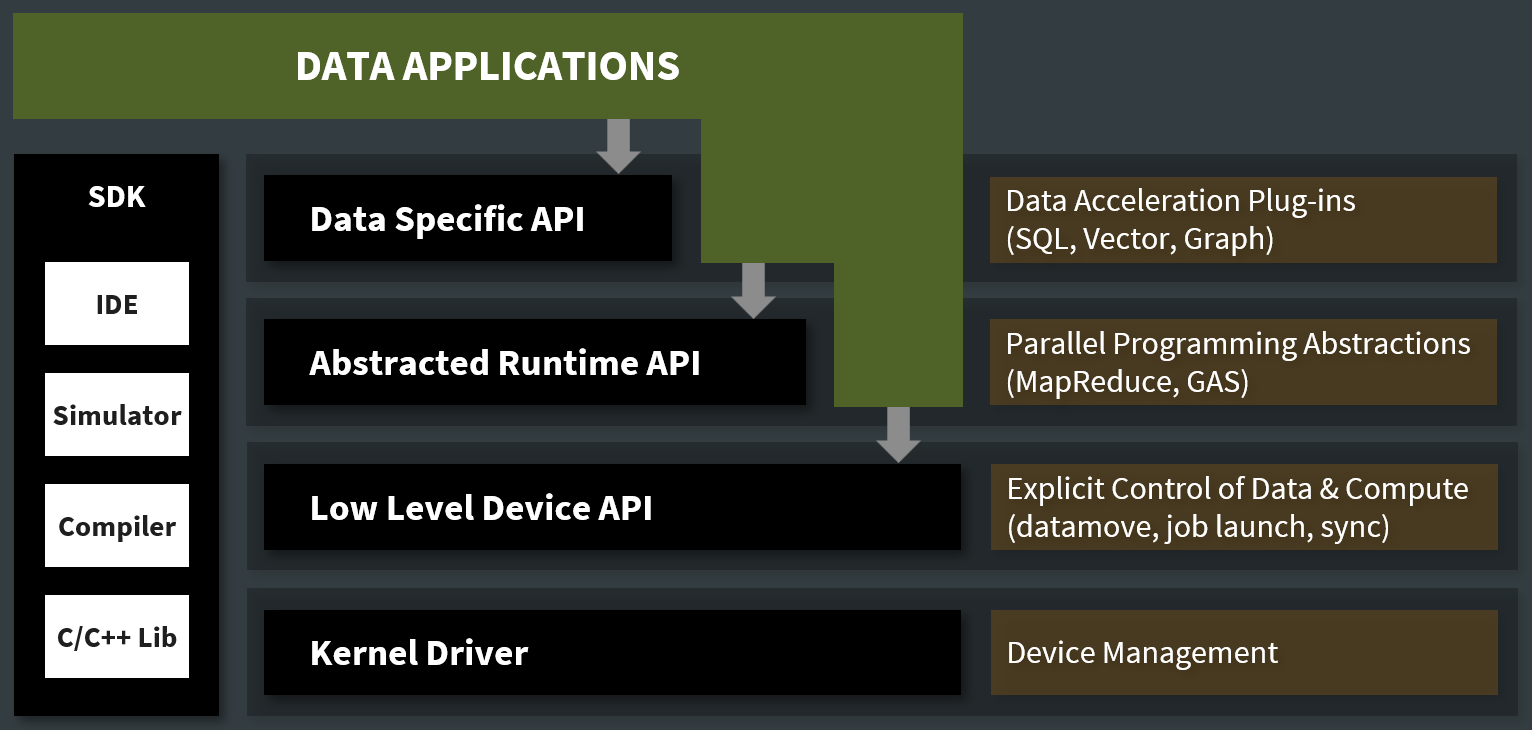

XCENA Software Development Kit (SDK) is a comprehensive software framework designed to facilitate easy and efficient utilization of XCENA hardware for data-intensive applications such as AI, machine learning, and real-time analytics. By providing multi-level APIs and a suite of development tools, the XCENA SDK allows for seamless integration with CXL computational memory, enabling developers to accelerate their applications with minimal effort.

Features

- Seamless integration with computational CXL memory, specialized for data-intensive applications such as AI, ML, and real-time analytics

- Multi-level APIs for flexible, efficient development

- Support for emulation and simulation with general tools like QEMU and our proprietary simulators, ensuring smooth development and testing environments

Software Ecosystem

- Applications: Main applications running on the host system that leverage XCENA hardware for enhanced performance.

- Computing Kernels: In-memory computing kernels for offloading data processing workloads from the host to the XCENA hardware.

- Parallel Xceleration Library (PXL): A library that facilitates optimized communication between the host and the device, ensuring efficient data transfer and task management.

- Linux Driver: A driver compatible with PXL that enables seamless interaction between the operating system and XCENA hardware.

- CLI Tool: A command-line utility for debugging and controlling XCENA devices, providing developers with direct access to device functionalities.

- Simulator: A software-defined simulator that models XCENA devices, allowing developers to develop and test applications in a virtual environment before deploying on actual hardware.

- QEMU Emulator: A customized QEMU emulator for running and debugging applications in environments without hardware.

Introduction

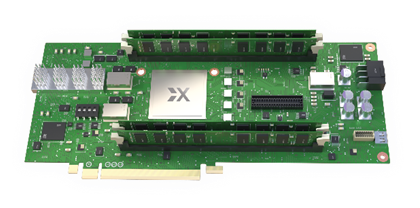

1. XCENA Hardware Architecture and MU core

XCENA’s computational memory features a multi-core architecture optimized for CXL-based memory expansion and near-memory computing. The SoC integrates thousands of processing units, called MUs, along with a vertically optimized cache structure, offering high performance parallel processing. Each MU is XCENA’s proprietary 64bit microprocessor based on RISC-V ISA.

In order to utilize thousands of MUs efficiently, XCENA’s computational resources are grouped into multiple computing subsystems, which are further subdivided into several clusters. One subsystem shares a common computing binary, enabling the MUs within the subsystem to execute the binary in parallel.

2. Memory Wall

The exponential increase in data is causing memory to become the biggest bottleneck in enhancing system performance and efficiency. Memory capacity is struggling to keep pace, creating inefficiencies and slowing down the entire system performance due to the need to move large amounts of data between the host and devices. Despite these limitations, memory remains one of the most expensive components in a server system, and its utilization is often low.

3. CXL

CXL (Compute Express Link) is the next-generation interconnect protocol that could bring in a data-centric paradigm to the existing computing system architecture. CXL provides high scalability for memory expansion, cache coherency to reduce redundant data movement, and heterogeneous computing infrastructure. It is now being spotlighted by the industry to become a comprehensive solution to break the ‘Memory Wall’ issue. Leveraging these CXL key features, XCENA introduces an advanced CXL device called CXL computational memory.

4. Computational Memory

XCENA CXL computational memory is a CXL 3.0, Type 3 device with Back Invalidation, supporting both CXL.io and CXL.mem protocols. It includes our own CXL controller and 1000s of proprietary RISC-V cores, on top of CXL DRAMs that can expand up to TB-scale of DDR5. By adding computational capabilities near memory, we aim to provide more than just memory expansion that general CXL players are providing, and enhance system efficiency even more by moving less data, using fewer CPUs, consuming less power, and reducing latency.

Contribution and Support

Will be updated.

License

XCENA SDK is licensed under Apache-2.0 license.